# ARM<sup>®</sup> Compiler Version 5.06

armasm User Guide

# **ARM®** Compiler

#### armasm User Guide

Copyright © 2010-2016 ARM Limited or its affiliates. All rights reserved.

**Release Information**

#### **Document History**

| Issue | Date              | Confidentiality  | Change                                           |

|-------|-------------------|------------------|--------------------------------------------------|

| А     | May 2010          | Non-Confidential | ARM Compiler v4.1 Release                        |

| В     | 30 September 2010 | Non-Confidential | Update 1 for ARM Compiler v4.1                   |

| С     | 28 January 2011   | Non-Confidential | Update 2 for ARM Compiler v4.1 Patch 3           |

| D     | 30 April 2011     | Non-Confidential | ARM Compiler v5.0 Release                        |

| Е     | 29 July 2011      | Non-Confidential | Update 1 for ARM Compiler v5.0                   |

| F     | 30 September 2011 | Non-Confidential | ARM Compiler v5.01 Release                       |

| G     | 29 February 2012  | Non-Confidential | Document update 1 for ARM Compiler v5.01 Release |

| Н     | 27 July 2012      | Non-Confidential | ARM Compiler v5.02 Release                       |

| Ι     | 31 January 2013   | Non-Confidential | ARM Compiler v5.03 Release                       |

| J     | 27 November 2013  | Non-Confidential | ARM Compiler v5.04 Release                       |

| K     | 10 September 2014 | Non-Confidential | ARM Compiler v5.05 Release                       |

| L     | 29 July 2015      | Non-Confidential | ARM Compiler v5.06 Release                       |

| М     | 11 November 2016  | Non-Confidential | Update 3 for ARM Compiler v5.06 Release          |

#### **Non-Confidential Proprietary Notice**

This document is protected by copyright and other related rights and the practice or implementation of the information contained in this document may be protected by one or more patents or pending patent applications. No part of this document may be reproduced in any form by any means without the express prior written permission of ARM. **No license, express or implied, by estoppel or otherwise to any intellectual property rights is granted by this document unless specifically stated.**

Your access to the information in this document is conditional upon your acceptance that you will not use or permit others to use the information for the purposes of determining whether implementations infringe any third party patents.

THIS DOCUMENT IS PROVIDED "AS IS". ARM PROVIDES NO REPRESENTATIONS AND NO WARRANTIES, EXPRESS, IMPLIED OR STATUTORY, INCLUDING, WITHOUT LIMITATION, THE IMPLIED WARRANTIES OF MERCHANTABILITY, SATISFACTORY QUALITY, NON-INFRINGEMENT OR FITNESS FOR A PARTICULAR PURPOSE WITH RESPECT TO THE DOCUMENT. For the avoidance of doubt, ARM makes no representation with respect to, and has undertaken no analysis to identify or understand the scope and content of, third party patents, copyrights, trade secrets, or other rights.

This document may include technical inaccuracies or typographical errors.

TO THE EXTENT NOT PROHIBITED BY LAW, IN NO EVENT WILL ARM BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION ANY DIRECT, INDIRECT, SPECIAL, INCIDENTAL, PUNITIVE, OR CONSEQUENTIAL DAMAGES, HOWEVER CAUSED AND REGARDLESS OF THE THEORY OF LIABILITY, ARISING OUT OF ANY USE OF THIS DOCUMENT, EVEN IF ARM HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES.

This document consists solely of commercial items. You shall be responsible for ensuring that any use, duplication or disclosure of this document complies fully with any relevant export laws and regulations to assure that this document or any portion thereof is not exported, directly or indirectly, in violation of such export laws. Use of the word "partner" in reference to ARM's customers is not intended to create or refer to any partnership relationship with any other company. ARM may make changes to this document at any time and without notice.

If any of the provisions contained in these terms conflict with any of the provisions of any signed written agreement covering this document with ARM, then the signed written agreement prevails over and supersedes the conflicting provisions of these terms. This document may be translated into other languages for convenience, and you agree that if there is any conflict between the English version of this document and any translation, the terms of the English version of the Agreement shall prevail.

Words and logos marked with <sup>®</sup> or <sup>™</sup> are registered trademarks or trademarks of ARM Limited or its affiliates in the EU and/or elsewhere. All rights reserved. Other brands and names mentioned in this document may be the trademarks of their respective owners. Please follow ARM's trademark usage guidelines at *http://www.arm.com/about/trademark-usage-guidelines.php*

Copyright © 2010-2016, ARM Limited or its affiliates. All rights reserved.

ARM Limited. Company 02557590 registered in England.

110 Fulbourn Road, Cambridge, England CB1 9NJ.

LES-PRE-20349

#### **Confidentiality Status**

This document is Non-Confidential. The right to use, copy and disclose this document may be subject to license restrictions in accordance with the terms of the agreement entered into by ARM and the party that ARM delivered this document to.

Unrestricted Access is an ARM internal classification.

#### **Product Status**

The information in this document is Final, that is for a developed product.

#### Web Address

http://www.arm.com

# Contents ARM<sup>®</sup> Compiler armasm User Guide

| Pref | ace                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | About this book                                                                                                                         | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Over | rview of the Assembler                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1.1  | About the ARM Compiler toolchain assemblers                                                                                             | 1-28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2  | Key features of the assembler                                                                                                           | 1-29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.3  | How the assembler works                                                                                                                 | 1-30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.4  | Directives that can be omitted in pass 2 of the assembler                                                                               | 1-32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Over | rview of the ARM Architecture                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2.1  | About the ARM architecture                                                                                                              | 2-35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2  | ARM, Thumb, and ThumbEE instruction sets                                                                                                | 2-36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3  | Changing between ARM, Thumb, and ThumbEE state                                                                                          | 2-37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.4  | Processor modes, and privileged and unprivileged software execution                                                                     | 2-38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.5  | Processor modes in ARMv6-M and ARMv7-M                                                                                                  | 2-39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.6  | NEON technology                                                                                                                         | 2-40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.7  | VFP hardware                                                                                                                            | 2-41                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.8  | ARM registers                                                                                                                           | 2-42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.9  | General-purpose registers                                                                                                               | 2-44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.10 | Register accesses                                                                                                                       | 2-45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.11 | Predeclared core register names                                                                                                         | 2-46                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.12 | Predeclared extension register names                                                                                                    | 2-47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.13 | Predeclared XScale register names                                                                                                       | 2-48                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.14 | Predeclared coprocessor names                                                                                                           | 2-49                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|      | Over<br>1.1<br>1.2<br>1.3<br>1.4<br>Over<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.6<br>2.7<br>2.8<br>2.9<br>2.10<br>2.11<br>2.12<br>2.13 | Overview of the Assembler         1.1       About the ARM Compiler toolchain assemblers         1.2       Key features of the assembler         1.3       How the assembler works         1.4       Directives that can be omitted in pass 2 of the assembler         Overview of the ARM Architecture         2.1       About the ARM architecture         2.2       ARM, Thumb, and ThumbEE instruction sets         2.3       Changing between ARM, Thumb, and ThumbEE state         2.4       Processor modes, and privileged and unprivileged software execution         2.5       Processor modes in ARMv6-M and ARMv7-M         2.6       NEON technology         2.7       VFP hardware         2.8       ARM registers         2.9       General-purpose registers         2.10       Register accesses         2.11       Predeclared core register names         2.12       Predeclared extension register names         2.13       Predeclared XScale register names |

|           | 2.15  | Program Counter                                                | 2-50  |

|-----------|-------|----------------------------------------------------------------|-------|

|           | 2.16  | Application Program Status Register                            | 2-51  |

|           | 2.17  | The Q flag                                                     | 2-52  |

|           | 2.18  | Current Program Status Register                                | 2-53  |

|           | 2.19  | Saved Program Status Registers                                 | 2-54  |

|           | 2.20  | ARM and Thumb instruction set overview                         | 2-55  |

|           | 2.21  | Access to the inline barrel shifter                            | 2-56  |

| Chapter 3 | Strue | cture of Assembly Language Modules                             |       |

|           | 3.1   | Syntax of source lines in assembly language                    | 3-58  |

|           | 3.2   | Literals                                                       | 3-60  |

|           | 3.3   | ELF sections and the AREA directive                            | 3-61  |

|           | 3.4   | An example ARM assembly language module                        | 3-62  |

| Chapter 4 | Writi | ing ARM Assembly Language                                      |       |

|           | 4.1   | About the Unified Assembler Language                           | 4-65  |

|           | 4.2   | Register usage in subroutine calls                             | 4-66  |

|           | 4.3   | Load immediate values                                          | 4-67  |

|           | 4.4   | Load immediate values using MOV and MVN                        | 4-68  |

|           | 4.5   | Load immediate values using MOV32                              | 4-69  |

|           | 4.6   | Load immediate values using LDR Rd, =const                     | 4-70  |

|           | 4.7   | Literal pools                                                  | 4-71  |

|           | 4.8   | Load addresses into registers                                  | 4-73  |

|           | 4.9   | Load addresses to a register using ADR                         |       |

|           | 4.10  | Load addresses to a register using ADRL                        |       |

|           | 4.11  | Load addresses to a register using LDR Rd, =label              |       |

|           | 4.12  | Other ways to load and store registers                         |       |

|           | 4.13  | Load and store multiple register instructions                  |       |

|           | 4.14  | Load and store multiple register instructions in ARM and Thumb |       |

|           | 4.15  | Stack implementation using LDM and STM                         |       |

|           | 4.16  | Stack operations for nested subroutines                        |       |

|           | 4.17  | Block copy with LDM and STM                                    |       |

|           | 4.18  | Memory accesses                                                |       |

|           | 4.19  | The Read-Modify-Write operation                                |       |

|           | 4.20  | Optional hash with immediate constants                         | 4-89  |

|           | 4.21  | Use of macros                                                  |       |

|           | 4.22  | Test-and-branch macro example                                  |       |

|           | 4.23  | Unsigned integer division macro example                        |       |

|           | 4.24  | Instruction and directive relocations                          |       |

|           | 4.25  | Symbol versions                                                |       |

|           | 4.26  | Frame directives                                               |       |

|           | 4.27  | Exception tables and Unwind tables                             |       |

|           | 4.28  | Assembly language changes after RVCT v2.1                      |       |

| Chapter 5 | Cond  | dition Codes                                                   |       |

|           | 5.1   | Conditional instructions                                       | 5-102 |

|           | 5.2   | Conditional execution in ARM state                             |       |

|           | 5.3   | Conditional execution in Thumb state                           |       |

|           | 5.4   | Updates to the condition flags                                 |       |

|           | 5.5   | Condition code suffixes and related flags                      |       |

|           |       |                                                                |       |

|           | 5.6  | Comparison of condition code meanings in integer and floating-point code | 5-107 |

|-----------|------|--------------------------------------------------------------------------|-------|

|           | 5.7  | Benefits of using conditional execution                                  | 5-109 |

|           | 5.8  | Example showing the benefits of using conditional instructions           | 5-110 |

|           | 5.9  | Optimization for execution speed                                         | 5-113 |

| Chapter 6 | Usin | g the Assembler                                                          |       |

|           | 6.1  | armasm command-line syntax                                               | 6-115 |

|           | 6.2  | Specify command-line options with an environment variable                |       |

|           | 6.3  | Using stdin to input source code to the assembler                        |       |

|           | 6.4  | Built-in variables and constants                                         |       |

|           | 6.5  | Identifying versions of armasm in source code                            |       |

|           | 6.6  | Diagnostic messages                                                      |       |

|           | 6.7  | Interlocks diagnostics                                                   |       |

|           | 6.8  | Automatic IT block generation                                            |       |

|           | 6.9  | Thumb branch target alignment                                            |       |

|           | 6.10 | Thumb code size diagnostics                                              |       |

|           | 6.11 | ARM and Thumb instruction portability diagnostics                        |       |

|           | 6.12 | Instruction width diagnostics                                            |       |

|           | 6.13 | Two pass assembler diagnostics                                           |       |

|           | 6.14 | Conditional assembly                                                     |       |

|           | 6.15 | Using the C preprocessor                                                 |       |

|           | 6.16 | Address alignment                                                        |       |

|           | 6.17 | Instruction width selection in Thumb                                     |       |

| Chapter 7 | 7.1  | bols, Literals, Expressions, and Operators Symbol naming rules           |       |

|           | 7.2  | Variables                                                                | 7-139 |

|           | 7.3  | Numeric constants                                                        | 7-140 |

|           | 7.4  | Assembly time substitution of variables                                  | 7-141 |

|           | 7.5  | Register-relative and PC-relative expressions                            | 7-142 |

|           | 7.6  | Labels                                                                   | 7-143 |

|           | 7.7  | Labels for PC-relative addresses                                         | 7-144 |

|           | 7.8  | Labels for register-relative addresses                                   | 7-145 |

|           | 7.9  | Labels for absolute addresses                                            | 7-146 |

|           | 7.10 | Numeric local labels                                                     | 7-147 |

|           | 7.11 | Syntax of numeric local labels                                           | 7-148 |

|           | 7.12 | String expressions                                                       | 7-149 |

|           | 7.13 | String literals                                                          | 7-150 |

|           | 7.14 | Numeric expressions                                                      | 7-151 |

|           | 7.15 | Syntax of numeric literals                                               | 7-152 |

|           | 7.16 | Syntax of floating-point literals                                        | 7-153 |

|           | 7.17 | Logical expressions                                                      | 7-154 |

|           | 7.18 | Logical literals                                                         | 7-155 |

|           | 7.19 | Unary operators                                                          | 7-156 |

|           | 7.20 | Binary operators                                                         | 7-157 |

|           | 7.21 | Multiplicative operators                                                 | 7-158 |

|           | 7.22 | String manipulation operators                                            | 7-159 |

|           | 7.23 | Shift operators                                                          | 7-160 |

|           | 7.24 | Addition, subtraction, and logical operators                             | 7-161 |

|           | 7.25 | Relational operators                                                     | 7-162 |

|           | 7.26                                                                                                                                                | Boolean operators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-163                                                                                                                                                                                                                                                                                                                                 |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 7.27                                                                                                                                                | Operator precedence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 7-164                                                                                                                                                                                                                                                                                                                                 |

|           | 7.28                                                                                                                                                | Difference between operator precedence in assembly language and C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7-165                                                                                                                                                                                                                                                                                                                                 |

| Chapter 8 | NEO                                                                                                                                                 | N Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                       |

|           | 8.1                                                                                                                                                 | Architecture support for NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-168                                                                                                                                                                                                                                                                                                                                 |

|           | 8.2                                                                                                                                                 | Half-precision extension for NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-169                                                                                                                                                                                                                                                                                                                                 |

|           | 8.3                                                                                                                                                 | Fused Multiply-Add extension for NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-170                                                                                                                                                                                                                                                                                                                                 |

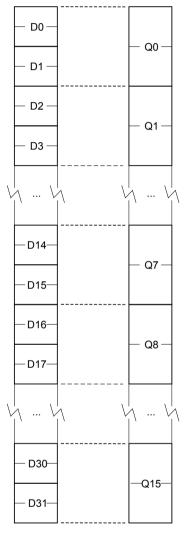

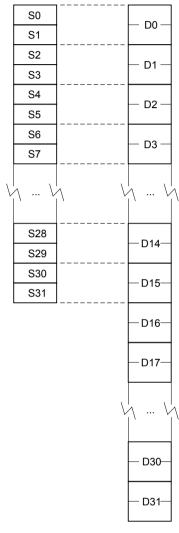

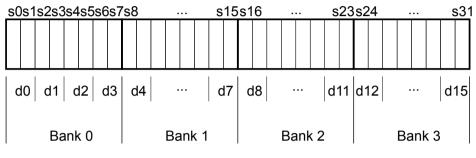

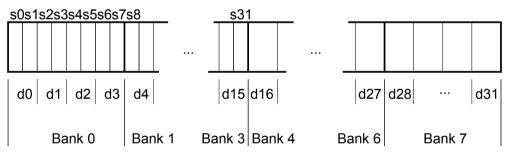

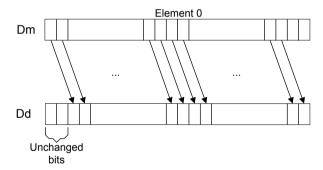

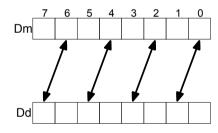

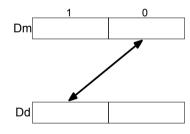

|           | 8.4                                                                                                                                                 | Extension register bank mapping in NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8-171                                                                                                                                                                                                                                                                                                                                 |

|           | 8.5                                                                                                                                                 | NEON views of the extension register bank                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 8-173                                                                                                                                                                                                                                                                                                                                 |

|           | 8.6                                                                                                                                                 | Load values to NEON registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-174                                                                                                                                                                                                                                                                                                                                 |

|           | 8.7                                                                                                                                                 | Conditional execution of NEON instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-175                                                                                                                                                                                                                                                                                                                                 |

|           | 8.8                                                                                                                                                 | Floating-point exceptions in NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8-176                                                                                                                                                                                                                                                                                                                                 |

|           | 8.9                                                                                                                                                 | NEON data types                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-177                                                                                                                                                                                                                                                                                                                                 |

|           | 8.10                                                                                                                                                | Extended notation extension for NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 8-178                                                                                                                                                                                                                                                                                                                                 |

|           | 8.11                                                                                                                                                | NEON vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-179                                                                                                                                                                                                                                                                                                                                 |

|           | 8.12                                                                                                                                                | Normal, long, wide, and narrow NEON operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8-180                                                                                                                                                                                                                                                                                                                                 |

|           | 8.13                                                                                                                                                | Saturating NEON instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-181                                                                                                                                                                                                                                                                                                                                 |

|           | 8.14                                                                                                                                                | NEON scalars                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8-182                                                                                                                                                                                                                                                                                                                                 |

|           | 8.15                                                                                                                                                | Polynomial arithmetic over {0,1}                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8-183                                                                                                                                                                                                                                                                                                                                 |

|           | 8.16                                                                                                                                                | NEON system registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8-184                                                                                                                                                                                                                                                                                                                                 |

|           | 8.17                                                                                                                                                | Flush-to-zero mode in NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-185                                                                                                                                                                                                                                                                                                                                 |

|           | 8.18                                                                                                                                                | NEON operations not affected by flush-to-zero mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8-186                                                                                                                                                                                                                                                                                                                                 |

|           | 8.19                                                                                                                                                | When to use flush-to-zero mode in NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8-187                                                                                                                                                                                                                                                                                                                                 |

|           | 8.20                                                                                                                                                | The effects of using flush-to-zero mode in NEON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 8-188                                                                                                                                                                                                                                                                                                                                 |

|           |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |

| Chapter 9 | VFP                                                                                                                                                 | Programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                       |

| Chapter 9 | <b>VFP</b><br>9.1                                                                                                                                   | Programming Architecture support for VFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9-191                                                                                                                                                                                                                                                                                                                                 |

| Chapter 9 |                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                       |

| Chapter 9 | 9.1                                                                                                                                                 | Architecture support for VFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9-192                                                                                                                                                                                                                                                                                                                                 |

| Chapter 9 | 9.1<br>9.2                                                                                                                                          | Architecture support for VFP<br>Half-precision extension for VFP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 9-192<br>9-193                                                                                                                                                                                                                                                                                                                        |